AI芯片电源的挑战

栏目:媒体新闻 发布时间:2025-07-07 19:28

随着人工智能工作负载(AI)变得更大,更复杂,开发了各种处理元素来处理所有这些数据...

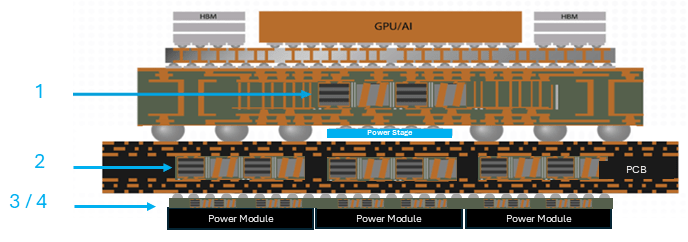

随着人工智能(AI)的工作负载变得更大,越来越复杂,为处理所有这些数据而开发的各种处理元素都需要不间断的功能。但是,此类电源的有效和可靠的交付,而无需降低信号的完整性或引入热瓶颈,这给半导体历史上的设计和制造带来了最严重的挑战。与一般目标处理器不同,专为人工智能工作负载设计的芯片将密度提高到极端水平。他们将更多的晶体管包装在较小的包装中,同时也增加了晶体管的总数,通常是以chi的形式。结果是一个较大,更强大的系统级软件包,其中电源不仅是电力问题,而且是集成材料和系统的挑战,该材料和系统从单个芯片延伸到服务器机架。 “力量更由动态变化的力量主导,主要是由计算和摘要研究员戈德温·马本(Godwin Maben)说,“记忆。它使良好的公交架构和现代体系结构(例如数据压缩技术)至关重要。由于内存和计算单元之间来回的大量数据穿梭,动态功能占主导地位。 These shipments have been made throughout the memory Using a variety of high -speed slow -slow hierarchies, all of these hierarchies use these different hierarchies,All of these hierarchies use these different hierarchies, all of these organizations move that all these hierarchies are moving all of these data, come at a cost, creating cascading design barriers that extend from hierarchy decisions of memory -operating networks (PDNs). “要处理到这些水平的电力传递,多学科设计团队必须完全考虑控制方法的位置和电压当前的应力以及在电气移民和IR下降之前的边距会影响可靠性。 EDA工具,监视ProcessEsfair和高级包装之间的轻量级集成。 Synopys首席建筑师Jay Roy说:“如今,高性能计算和AI加速器已经越过了千瓦的边界。” “设计和缩短周期的复杂性的爆炸性增长提出了半导体SOC设计中的持续挑战。”这推动了扩大性能的推动力,同时降低电力消耗会迫使电力传输模式发生重大变化。这不仅减少了拖动。这涉及对具有不同膨胀系数的材料之间的诱导,热梯度和整合。现在对电压滴,当前的瓶颈和热热点的早期预测至关重要,应该在实际的布局和集成障碍的背景下进行。从侧面到In没有模拟的价值可以解决传统供应侧面自然限制的垂直供应。整个软件包和印刷电路电路板的高电流供应流将带来不再扩大的损失和空间限制。当芯片消耗100或200个WAT小时时,此方法是可行的,但是现在它已成为现代AI硬件的限制因素。 Saras Micro Device的首席商业官员Eelco Bergman说:“目前的加速器卡通常使用侧面架构,从电力模块到处理器,这些架构在PCB痕迹的几厘米处损坏了数千台电流。” “此过程导致大量的停电和由于高波和痕量阻力引起的大量加热。此外,董事会空间将下注以支持日益增长的总功率,电力铁路数量以及高速信号的关键车辙。图1:垂直驱动的网络,显示了多型障碍物模块,该网络直接embedded theo软件包基板。被淘汰。具有低阻抗路径的垂直,从资源到硅的距离大大降低。 “这些方法没有顶级PCB空间,减少寄生损失并改善电源的整体性能。”在基板和插入器上使用集成电源层以及本地衰减,可为AI chiplets和加速器提供更清洁,更强大的功率,同时减少衰减。高级底物,包括具有宝石被动设备的底物,现在采用硅硅本设计,以优化阻抗和散热的曲线。同时,这些技术还为可靠性带来了新的挑战。通过新材料和垂直结构提供的大波浪需要严格对当前拥塞,热循环和材料疲劳进行严格建模。出现的功率组件应承受强大的热作用,同时还可以保持与敏感信号层的电分离。这反过来,推动了介电材料,去除技术和合作设计方法的变化。高强度密度的高级包装和热量耗散直接转化为热量密度,这可能导致热区域,从而降低可靠性和性能。如果没有获得热量的先进技术,即使是最有效的系统也需要热门节流,这可以降低性能。 “现在,先进的包装使用多尺度的热管理技术来有效地促进和去除热量,” Amkor Chip Small and Flip Chip Ball网格阵列(FCBGA)商业部高级总监Gerard John解释说。 “由于高温电导率约为80 W/m-k,依赖性合金TIM特别有效。但是,impium tim需要在芯片的背面和底部进行金属化,并且经常使用Ti/au或ni/au之类的材料。经常使用反射过程。需要在芯片和盖子之间形成键e。加工对于在整个芯片中实现恒定的热量衰减至关重要。设备的过程和筛选。这些解决方案通常装有特定的工作负载。例如,与理解相比,AI训练会产生更长的连续连续爆炸,并且需要多种热瞬态响应。包装工程师应与系统架构师合作,以确保冷却解决方案与实际的调整文件匹配。约翰说:“蒂姆的选择通常基于显示高热量生成区域的设备功率图。” “通过在这些映射中匹配TIM的性质,可以实现最佳的热管理,从而确保整个设备中良好的热量消散。”在多芯片系统中,靠近热逻辑模块会增强热挑战。先进的设计转移到温度霍顿板,微流体冷却和双面热提取以管理复杂性。每种方法都引入了制造的新障碍具有可靠性,可靠性和材料集成,但它们很快成为实现AI性能的重要工具。作为AI加速器的钼和材料转移需要更大的强度和更轻的整合,传统的前材料显示它们的老化。钨和铜被广泛用于当地连贯,接触始终是其电导率和劳动的行业标准,但现在对芯片最差的部分施加限制。这是钼成为主要替代金属的地方。钼的平均自由路径比铜的平均自由路径短,在狭窄几何形状上的可伸缩性比钨具有更好的可伸缩性,并且在电阻率和产生晚期节点方面的可伸缩性明显提高。副总裁兼总经理LAM Research副总裁Kaihan Ashtiani说:“从传统的钨金属化到钼的过渡可显着改善绩效,包括将接触电阻降低多达50%。” “钼具有较短的电子平均自由路径,使其更适合较小的尺寸,这大大减少了对严格组织的互连结构的抵抗力。在AI设备的限制中,这种属性越来越重要。在剪切的织物中常见E Ashtiani说:“ E降低了金属(例如铜等金属的平均自由路径)的平均自由路径会增加电阻,” Ashtiani说:“在这些情况下,诸如钼等金属具有较短的平均自由途径,实际上是更有用的,因为它保持了较小规模的较低电阻。 "Transfer to the molybdenum is also in accordance with the broader efforts of industries to reduce electromigration risks. In high current densities commonly found in AI workloads, the transfer of metal creates voids and open circuits over time. The high point of melting of molybdenum and grain stability will help offset it, making it a strong candidate for long -term AI computing applications. device containing back-powered power, where complementDo of the金属化层需要完全调整和低电阻率材料。通过竞争金属空间的顶层信号,BSPDN通过在晶圆下引入电气连接来分解这些功能。最初的概念最初被转换为英特尔的“权力VIA”,此后开发了整个行业中采用的更广泛的技术类别。从本质上讲,晶圆的背面被蚀刻以暴露接触,然后通过避免堆栈的信号途径并显着提高效率来直接赋予晶体管。 IMEC的Ryckäert说:“背面的电源是通过硅通过硅从后部提供直接电源来提供直接电源的力量,这有助于减少阻抗。首先,通过分开电源和信号电缆,EngiNEER在布局计划和时机的时机方面具有更大的灵活性。电源分布。n红外崩溃并使电压调节更具可预测性。 Ryckaert补充说:“电动输送曾经有很多考虑因素。” “现在它塑造了整个平面图。后面的PDN有助于缓解电缆的拥塞并实现更高的晶体管密度,但它们也增加了电力密度,使电力密度比其他方面更为重要。障碍物可以实施双面的策略,在该策略中,在两边的热接口中,在两边的热接口中,在两侧的两个侧面相互作用中,这是两侧相互作用的,这是两次相互互动的,在两个侧面相互互动,在两次相互作用中,在两侧相互作用,在两侧相互作用,在两侧相互作用,在两侧相互作用,在两个方面,在两侧相互作用,在两侧相互作用,在两侧相互作用,在两侧相互作用,在两侧相互作用,在两侧相互作用,这是两侧相互互动的。反向电源并不是一个挑战。仍在学习中,尽管有前途的技术前景,但收获的收获仍然是对与系统合作设计的障碍。,molibdenum互连和垂直PDN,这些进步都没有在分离中发生。下一代AI芯片将使用通常称为系统技术协作优化(STCO)的堆栈设计更轻的集成方法。在此模型中,芯片建筑师,包装工程师和系统设计师从第一个设计阶段开始工作。交付网络,热分布,机械压力和平面图应作为相互关联的系统建模,而不是连续的过程步骤。 Synopys的Maben说:“电力合作的设计变得越来越重要。它有助于平衡热能性能与场景的时间安排,从而使客户能够在最终产品中实现更高的效率和可靠性。在系统级别上,这些优化具有广泛的后果。当地的供暖,设计良好的系统在农场上的执行效果不佳。不仅仅是模具。TE和PCB)。如果良好的芯片能量按预期在实际应用中运行,则信号完整性,去耦水平的解耦和住房水平会影响所有情况。这些障碍增加了协作模拟和跨域反馈循环的重要性。现在,电压(EMI)的电压和干扰的完整性直接通过热模拟,材料建模和电意识验证。作为回应,一些CHIP制造商将团队带到室内工程系统或将其嵌入芯片设计团队中,以加快复发并确保一致性。除了技术协调外,经济激励措施还促进合作。通过添加过量的电容器,更宽的功率层或设计过度的VRM来过度配置咖喱供应收缩期,可以消费板区域和资源,否则可以用于计算。 “降低红外崩溃并提高交付效率直接转化为更少的热量成本萨拉斯(Saras)的伯格曼(Bergman)说,“这是高度数据中心成本的直接优势。该行业应该考虑从材料到平面材料,与预防热量的晶体结合。消失了。PLEX,通过性能,效率和可扩展性衡量的奖励将是巨大的。

随着人工智能(AI)的工作负载变得更大,越来越复杂,为处理所有这些数据而开发的各种处理元素都需要不间断的功能。但是,此类电源的有效和可靠的交付,而无需降低信号的完整性或引入热瓶颈,这给半导体历史上的设计和制造带来了最严重的挑战。与一般目标处理器不同,专为人工智能工作负载设计的芯片将密度提高到极端水平。他们将更多的晶体管包装在较小的包装中,同时也增加了晶体管的总数,通常是以chi的形式。结果是一个较大,更强大的系统级软件包,其中电源不仅是电力问题,而且是集成材料和系统的挑战,该材料和系统从单个芯片延伸到服务器机架。 “力量更由动态变化的力量主导,主要是由计算和摘要研究员戈德温·马本(Godwin Maben)说,“记忆。它使良好的公交架构和现代体系结构(例如数据压缩技术)至关重要。由于内存和计算单元之间来回的大量数据穿梭,动态功能占主导地位。 These shipments have been made throughout the memory Using a variety of high -speed slow -slow hierarchies, all of these hierarchies use these different hierarchies,All of these hierarchies use these different hierarchies, all of these organizations move that all these hierarchies are moving all of these data, come at a cost, creating cascading design barriers that extend from hierarchy decisions of memory -operating networks (PDNs). “要处理到这些水平的电力传递,多学科设计团队必须完全考虑控制方法的位置和电压当前的应力以及在电气移民和IR下降之前的边距会影响可靠性。 EDA工具,监视ProcessEsfair和高级包装之间的轻量级集成。 Synopys首席建筑师Jay Roy说:“如今,高性能计算和AI加速器已经越过了千瓦的边界。” “设计和缩短周期的复杂性的爆炸性增长提出了半导体SOC设计中的持续挑战。”这推动了扩大性能的推动力,同时降低电力消耗会迫使电力传输模式发生重大变化。这不仅减少了拖动。这涉及对具有不同膨胀系数的材料之间的诱导,热梯度和整合。现在对电压滴,当前的瓶颈和热热点的早期预测至关重要,应该在实际的布局和集成障碍的背景下进行。从侧面到In没有模拟的价值可以解决传统供应侧面自然限制的垂直供应。整个软件包和印刷电路电路板的高电流供应流将带来不再扩大的损失和空间限制。当芯片消耗100或200个WAT小时时,此方法是可行的,但是现在它已成为现代AI硬件的限制因素。 Saras Micro Device的首席商业官员Eelco Bergman说:“目前的加速器卡通常使用侧面架构,从电力模块到处理器,这些架构在PCB痕迹的几厘米处损坏了数千台电流。” “此过程导致大量的停电和由于高波和痕量阻力引起的大量加热。此外,董事会空间将下注以支持日益增长的总功率,电力铁路数量以及高速信号的关键车辙。图1:垂直驱动的网络,显示了多型障碍物模块,该网络直接embedded theo软件包基板。被淘汰。具有低阻抗路径的垂直,从资源到硅的距离大大降低。 “这些方法没有顶级PCB空间,减少寄生损失并改善电源的整体性能。”在基板和插入器上使用集成电源层以及本地衰减,可为AI chiplets和加速器提供更清洁,更强大的功率,同时减少衰减。高级底物,包括具有宝石被动设备的底物,现在采用硅硅本设计,以优化阻抗和散热的曲线。同时,这些技术还为可靠性带来了新的挑战。通过新材料和垂直结构提供的大波浪需要严格对当前拥塞,热循环和材料疲劳进行严格建模。出现的功率组件应承受强大的热作用,同时还可以保持与敏感信号层的电分离。这反过来,推动了介电材料,去除技术和合作设计方法的变化。高强度密度的高级包装和热量耗散直接转化为热量密度,这可能导致热区域,从而降低可靠性和性能。如果没有获得热量的先进技术,即使是最有效的系统也需要热门节流,这可以降低性能。 “现在,先进的包装使用多尺度的热管理技术来有效地促进和去除热量,” Amkor Chip Small and Flip Chip Ball网格阵列(FCBGA)商业部高级总监Gerard John解释说。 “由于高温电导率约为80 W/m-k,依赖性合金TIM特别有效。但是,impium tim需要在芯片的背面和底部进行金属化,并且经常使用Ti/au或ni/au之类的材料。经常使用反射过程。需要在芯片和盖子之间形成键e。加工对于在整个芯片中实现恒定的热量衰减至关重要。设备的过程和筛选。这些解决方案通常装有特定的工作负载。例如,与理解相比,AI训练会产生更长的连续连续爆炸,并且需要多种热瞬态响应。包装工程师应与系统架构师合作,以确保冷却解决方案与实际的调整文件匹配。约翰说:“蒂姆的选择通常基于显示高热量生成区域的设备功率图。” “通过在这些映射中匹配TIM的性质,可以实现最佳的热管理,从而确保整个设备中良好的热量消散。”在多芯片系统中,靠近热逻辑模块会增强热挑战。先进的设计转移到温度霍顿板,微流体冷却和双面热提取以管理复杂性。每种方法都引入了制造的新障碍具有可靠性,可靠性和材料集成,但它们很快成为实现AI性能的重要工具。作为AI加速器的钼和材料转移需要更大的强度和更轻的整合,传统的前材料显示它们的老化。钨和铜被广泛用于当地连贯,接触始终是其电导率和劳动的行业标准,但现在对芯片最差的部分施加限制。这是钼成为主要替代金属的地方。钼的平均自由路径比铜的平均自由路径短,在狭窄几何形状上的可伸缩性比钨具有更好的可伸缩性,并且在电阻率和产生晚期节点方面的可伸缩性明显提高。副总裁兼总经理LAM Research副总裁Kaihan Ashtiani说:“从传统的钨金属化到钼的过渡可显着改善绩效,包括将接触电阻降低多达50%。” “钼具有较短的电子平均自由路径,使其更适合较小的尺寸,这大大减少了对严格组织的互连结构的抵抗力。在AI设备的限制中,这种属性越来越重要。在剪切的织物中常见E Ashtiani说:“ E降低了金属(例如铜等金属的平均自由路径)的平均自由路径会增加电阻,” Ashtiani说:“在这些情况下,诸如钼等金属具有较短的平均自由途径,实际上是更有用的,因为它保持了较小规模的较低电阻。 "Transfer to the molybdenum is also in accordance with the broader efforts of industries to reduce electromigration risks. In high current densities commonly found in AI workloads, the transfer of metal creates voids and open circuits over time. The high point of melting of molybdenum and grain stability will help offset it, making it a strong candidate for long -term AI computing applications. device containing back-powered power, where complementDo of the金属化层需要完全调整和低电阻率材料。通过竞争金属空间的顶层信号,BSPDN通过在晶圆下引入电气连接来分解这些功能。最初的概念最初被转换为英特尔的“权力VIA”,此后开发了整个行业中采用的更广泛的技术类别。从本质上讲,晶圆的背面被蚀刻以暴露接触,然后通过避免堆栈的信号途径并显着提高效率来直接赋予晶体管。 IMEC的Ryckäert说:“背面的电源是通过硅通过硅从后部提供直接电源来提供直接电源的力量,这有助于减少阻抗。首先,通过分开电源和信号电缆,EngiNEER在布局计划和时机的时机方面具有更大的灵活性。电源分布。n红外崩溃并使电压调节更具可预测性。 Ryckaert补充说:“电动输送曾经有很多考虑因素。” “现在它塑造了整个平面图。后面的PDN有助于缓解电缆的拥塞并实现更高的晶体管密度,但它们也增加了电力密度,使电力密度比其他方面更为重要。障碍物可以实施双面的策略,在该策略中,在两边的热接口中,在两边的热接口中,在两侧的两个侧面相互作用中,这是两侧相互作用的,这是两次相互互动的,在两个侧面相互互动,在两次相互作用中,在两侧相互作用,在两侧相互作用,在两侧相互作用,在两侧相互作用,在两个方面,在两侧相互作用,在两侧相互作用,在两侧相互作用,在两侧相互作用,在两侧相互作用,在两侧相互作用,这是两侧相互互动的。反向电源并不是一个挑战。仍在学习中,尽管有前途的技术前景,但收获的收获仍然是对与系统合作设计的障碍。,molibdenum互连和垂直PDN,这些进步都没有在分离中发生。下一代AI芯片将使用通常称为系统技术协作优化(STCO)的堆栈设计更轻的集成方法。在此模型中,芯片建筑师,包装工程师和系统设计师从第一个设计阶段开始工作。交付网络,热分布,机械压力和平面图应作为相互关联的系统建模,而不是连续的过程步骤。 Synopys的Maben说:“电力合作的设计变得越来越重要。它有助于平衡热能性能与场景的时间安排,从而使客户能够在最终产品中实现更高的效率和可靠性。在系统级别上,这些优化具有广泛的后果。当地的供暖,设计良好的系统在农场上的执行效果不佳。不仅仅是模具。TE和PCB)。如果良好的芯片能量按预期在实际应用中运行,则信号完整性,去耦水平的解耦和住房水平会影响所有情况。这些障碍增加了协作模拟和跨域反馈循环的重要性。现在,电压(EMI)的电压和干扰的完整性直接通过热模拟,材料建模和电意识验证。作为回应,一些CHIP制造商将团队带到室内工程系统或将其嵌入芯片设计团队中,以加快复发并确保一致性。除了技术协调外,经济激励措施还促进合作。通过添加过量的电容器,更宽的功率层或设计过度的VRM来过度配置咖喱供应收缩期,可以消费板区域和资源,否则可以用于计算。 “降低红外崩溃并提高交付效率直接转化为更少的热量成本萨拉斯(Saras)的伯格曼(Bergman)说,“这是高度数据中心成本的直接优势。该行业应该考虑从材料到平面材料,与预防热量的晶体结合。消失了。PLEX,通过性能,效率和可扩展性衡量的奖励将是巨大的。